Motorola MVME2400 Series Installation And Use Manual

Vme processor module

Hide thumbs

Also See for MVME2400 Series:

- Programmer's reference manual (331 pages) ,

- Installation and user manual (20 pages)

Table of Contents

Table of Contents

Summary of Contents for Motorola MVME2400 Series

- Page 1 MVME2400 Series VME Processor Module Installation and Use V2400A/IH3 August 2001...

- Page 2 Motorola, Inc. ® PowerPC is a registered trademark and AIX , PowerPC 603 , and PowerPC 604 trademarks of International Business Machines Corporation and are used by Motorola, Inc. under license from International Business Machines Corporation. ® ® ® SNAPHAT...

- Page 3 The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

- Page 4 Flammability All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers. EMI Caution This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

- Page 5 Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group web site. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

- Page 6 If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc. Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov.

-

Page 7: Table Of Contents

Contents About This Manual Summary of Changes ....................xvi Overview of Contents ....................xvi Comments and Suggestions ..................xvii Conventions Used in This Manual................xviii CHAPTER 1 Hardware Preparation and Installation Introduction........................1-1 Description .........................1-1 MVME240x Module...................1-2 PMCspan Expansion Mezzanine ................1-2 PCI Mezzanine Cards (PMCs)................1-3 VMEsystem Enclosure ..................1-3 System Console Terminal ...................1-3 Overview of Start-Up Procedures ................1-4... - Page 8 Switches......................2-3 ABT (S1) ..................... 2-3 RST (S2)...................... 2-3 Front Panel Indicators (DS1 – DS4)..............2-4 BFL (DS1)....................2-4 CPU (DS2) ....................2-4 PMC2 (DS3)....................2-4 PMC1 (DS4)....................2-4 10/100BaseT Port ....................2-5 DEBUG Port....................... 2-5 PMC Slots......................2-7 PCI MEZZANINE CARD (PMC Slot 1)............ 2-7 PCI MEZZANINE CARD (PMC Slot 2)............

- Page 9 Asynchronous Debug Port ................3-23 PCI-ISA Bridge (PIB) Controller ..............3-23 Real-Time Clock/NVRAM/Timer Function .............3-24 PCI Host Bridge (PHB) ..................3-25 Interrupt Controller (MPIC)................3-25 Programmable Timers..................3-26 Interval Timers ..................3-26 16/32-Bit Timers..................3-26 CHAPTER 4 Programming Details Introduction........................4-1 Memory Maps ......................4-1 Processor Bus Memory Map................4-2 Default Processor Memory Map..............4-2 PCI Local Bus Memory Map................4-3 VMEbus Memory Map ..................4-3...

- Page 10 PCI Mezzanine Card Connectors – J11 through J14........B-14 PCI Mezzanine Card Connectors – J21 through J24........B-17 APPENDIX C Troubleshooting Solving Startup Problems ..................C-1 APPENDIX D Related Documentation Motorola Computer Group Documents ..............D-1 Manufacturers’ Documents ..................D-2 Related Specifications ....................D-4...

- Page 11 List of Figures Figure 1-1. MVME2400 Switches, Headers, Connectors, Fuses, LEDs ....1-8 Figure 1-2. Software-Readable Header..............1-10 Figure 1-3. Typical Single-width PMC Module Placement on MVME240x ..1-14 Figure 1-4. PMCspan-002 Installation on an MVME240x ........1-16 Figure 1-5. PMCspan-010 Installation on a PMCspan-002/MVME240x ....1-18 Figure 2-1.

- Page 13 Table B-9. J21 and J22 PMC2 Connector Pin Assignments ......... B-17 Table B-10. J23 and J24 PMC2 Connector Pin Assignments ....... B-18 Table C-1. Troubleshooting MVME240x Modules ..........C-1 Table D-1. Motorola Computer Group Documents ..........D-1 Table D-2. Manufacturers’ Documents ..............D-2 Table D-3. Related Specifications ................D-4...

- Page 15 About This Manual The MVME2400 Series VME Processor Modules Installation and Use manual provides information to install and use your MVME2400 Series VME Processor Modules. As of the publication date, the information presented in this manual applies to the following MVME2400 series models:...

-

Page 16: Summary Of Changes

Overview of Contents Chapter 1, Hardware Preparation and Installation, provides a brief description of the MVME2400 Series VME Processor Module along with instructions for preparing and installing the hardware. Chapter 2, Operating Instructions, provides operating instructions for the... -

Page 17: Comments And Suggestions

Documentation, includes all documentation related to the MVME2400. Comments and Suggestions Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:... -

Page 18: Conventions Used In This Manual

Conventions Used in This Manual The following typographical conventions are used in this document: Unless otherwise specified, all address references are in hexadecimal. An asterisk (*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low. An asterisk (*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition. - Page 19 In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false.

-

Page 21: Introduction

1Hardware Preparation and Installation Introduction This chapter provides a brief description of the MVME2400 Series VME Processor Module. It also provides instructions for preparing and installing the hardware.Unless otherwise specified, the designation “MVME240x” refers to all models of the MVME2400 series modules. -

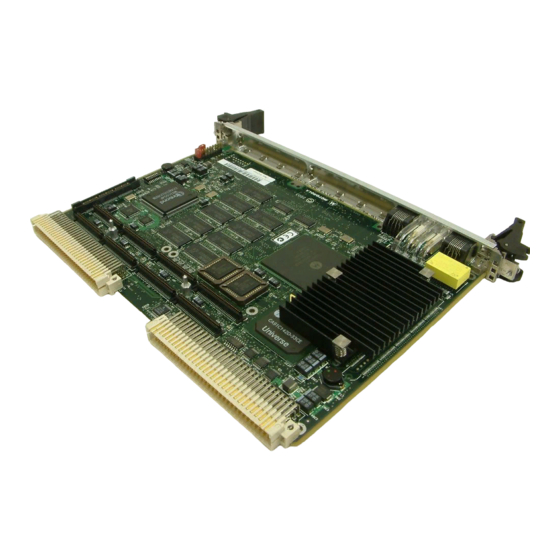

Page 22: Mvme240X Module

Hardware Preparation and Installation MVME240x Module The MVME240x is a powerful, low-cost embedded VME controller and intelligent PMC carrier board. It includes support circuitry such as ECC SDRAM, PROM/Flash memory, and bridges to the Industry Standard Architecture (ISA) bus and the VMEbus. The unit’s PMC carrier architecture allows flexible configuration options and easy upgrades. -

Page 23: Pci Mezzanine Cards (Pmcs)

System Console Terminal In normal operation, connection of a debug console terminal is required only if you intend to use the MVME240x’s debug firmware, PPCBug, interactively. An RJ-45 connector is provided on the front panel of the MVME240x for this purpose. http://www.motorola.com/computer/literature... -

Page 24: Overview Of Start-Up Procedures

Hardware Preparation and Installation Overview of Start-Up Procedures The following table lists the things you will need to do before you can use this board, and tells where to find the information you need to perform each step. Read this chapter in its entirety along with all Caution and Warning notes before beginning. - Page 25 Chapter 4, Programming Details your applications. For additional information on PMCs, refer to the PMC manuals provided with these cards. You may also wish to obtain the MVME2400 Series VME Processor Module Programmer’s Reference Guide, listed in Appendix D, Related Documentation.

-

Page 26: Unpacking Instructions

The MVME2400 control registers are described Chapter 3, Functional Description, and/or in the MVME2400 Series VME Processor Module Programmer’s Reference Guide listed under Appendix D, Related Documentation. -

Page 27: Mvme2400 Base Board Preparation

System Controller Selection (J9) on page 1-9 Software-Readable Header (SRH) Switch (S3) on page 1-10 The MVME240x has been factory tested and is shipped with the configurations described in the following sections. The MVME240x factory-installed debug monitor, PPCBug, operates with those factory settings. http://www.motorola.com/computer/literature... -

Page 28: Figure 1-1. Mvme2400 Switches, Headers, Connectors, Fuses, Leds

Hardware Preparation and Installation MVME 240x 1 2 3 4 5 6 7 8 Figure 1-1. MVME2400 Switches, Headers, Connectors, Fuses, LEDs Computer Group Literature Center Web Site... -

Page 29: Flash Bank Selection (J8)

Remove the jumper from J9 if you intend to operate the MVME240x as system controller in all cases. Install the jumper across pins 1 and 2 if the MVME240x will not to operate as system controller under any circumstances. http://www.motorola.com/computer/literature... -

Page 30: Software-Readable Header (Srh) Switch (S3)

SRH, and SRH Register Bit 7 is associated with Pin 8 and Pin 9 of the SRH. The SRH is a read-only register. If Motorola’s PowerPC firmware, PPCBug, is being used, it reserves all bits, SRH0 to SRH7. If it is not being used, the switch can be used for other applications. -

Page 31: Pmc Preparation

Eight bits per character One stop bit per character Parity disabled (no parity) Baud rate = 9600 baud (default baud rate of the port at power-up); after power-up, you can reconfigure the baud rate with PPCBug’s PF command http://www.motorola.com/computer/literature 1-11... -

Page 32: Hardware Installation

PMCspan modules onto the MVME240x, installing the MVME240x into a VME chassis, and connecting an optional system console terminal. Motorola strongly recommends that you use an antistatic wrist strap and a Use ESD conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). - Page 33 PMC module on top of the MVME240x. The four connectors on the underside of the PMC module should then connect smoothly with the corresponding connectors for a single-width PMC (J11/J12/J13/J14 or J21/J22/J23/J24, all eight for a double-width PMC) on the MVME240x. http://www.motorola.com/computer/literature 1-13...

-

Page 34: Primary Pmcspan Installation

Hardware Preparation and Installation Figure 1-3. Typical Single-width PMC Module Placement on MVME240x 6. Insert the two short Phillips screws through the holes at the forward corners of the PMC module, into the standoffs on the MVME240x. Tighten the screws. 7. - Page 35 – Insert the threaded end into the standoff hole at each corner of the VME processor module. – Thread the locking nuts onto the standoff tips. – Tighten the nuts with a box-end wrench or a pair of needle nose pliers. http://www.motorola.com/computer/literature 1-15...

-

Page 36: Figure 1-4. Pmcspan-002 Installation On An Mvme240X

Hardware Preparation and Installation 2081 9708 Figure 1-4. PMCspan-002 Installation on an MVME240x 1-16 Computer Group Literature Center Web Site... -

Page 37: Secondary Pmcspan Installation

2. Perform an operating system shutdown. Turn the AC or DC power off and remove the AC cord or DC power lines from the system. Remove chassis or system cover(s) as necessary for access to the VME modules. http://www.motorola.com/computer/literature 1-17... -

Page 38: Figure 1-5. Pmcspan-010 Installation On A Pmcspan-002/Mvme240X

Hardware Preparation and Installation 2065 9708 Figure 1-5. PMCspan-010 Installation on a PMCspan-002/MVME240x 1-18 Computer Group Literature Center Web Site... - Page 39 PMCspan-010 and into the standoffs on the primary PMCspan- 002. Tighten the screws. Note The screws have two different head diameters. Use the screws with the smaller heads on the standoffs next to VMEbus connectors P1 and P2. http://www.motorola.com/computer/literature 1-19...

-

Page 40: Mvme240X Installation

Hardware Preparation and Installation MVME240x Installation Before installing the MVME240x into your VME chassis, ensure that the jumpers on the MVME240x J8, J9, and S3 switch are configured, as previously described. This procedure assumes that you have already installed the PMCspan(s) if desired, and any PMCs that you have selected. Proceed as follows to install the MVME240x in the VME chassis: 1. - Page 41 RF emissions. Note Some VME backplanes (for example, those used in Motorola “Modular Chassis” systems) have an auto-jumpering feature for automatic propagation of the IACK and BG signals. Step does not apply to such backplane designs.

-

Page 42: System Considerations

Hardware Preparation and Installation System Considerations The MVME240x draws power from the VMEbus backplane connectors P1 and P2. P2 is also used for the upper 16 bits of data in 32-bit transfers, and for the upper eight address lines in extended addressing mode. The MVME240x may not function properly without its main board connected to VMEbus backplane connectors P1 and P2. - Page 43 System Considerations one MVME240x processor to broadcast a signal to any other MVME240x processors. All eight registers are accessible from any local processor as well as from the VMEbus. http://www.motorola.com/computer/literature 1-23...

-

Page 45: Overview

2Operating Instructions Overview This chapter provides operating instructions for the MVME240x. This includes information about powering up the system, and functionality of the switches, status indicators, and I/O ports on the front panels of the MVME240x and PMCspan modules. Applying Power After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that the installation is complete, you can power up the system. -

Page 46: Figure 2-1. Ppcbug Firmware System Startup

Operating Instructions Power-up/reset initialization STARTUP Initialize devices on the MVME240x INITIALIZATION module/system Power On Self Test diagnostics POST Firmware-configured boot mechanism, BOOTING if so configured. Default is no boot. Interactive, command-driven on-line PowerPC MONITOR debugger, when terminal connected. Figure 2-1. PPCBug Firmware System Startup Computer Group Literature Center Web Site... -

Page 47: Switches

SYSRESET*. A SYSRESET* signal may be generated by the RESET switch, a power-up reset, a watchdog timeout, or by a control bit in the Miscellaneous Control Register (MISC_CTL) in the Universe ASIC. SYSRESET* remains asserted for at least 200 ms, as required by the VMEbus specification. http://www.motorola.com/computer/literature... -

Page 48: Front Panel Indicators (Ds1 - Ds4)

Operating Instructions Front Panel Indicators (DS1 – DS4) MVME There are four LED (light-emitting diode) front panel 240x indicators located on the MVME240x front panel: BFL, , and PMC2 PMC1 BFL (DS1) The yellow LED indicates board failure; lights when the BRDFAIL* signal line is active. -

Page 49: 10/100Baset Port

Baud rate = 9600 baud (default baud rate at power-up) After power-up, the baud rate of the port can be reconfigured by DEBUG using the debugger’s Port Format (PF) command. Refer to Chapter 5, PPCBug Chapter 6, Environment Modification for information about the PPCBug. http://www.motorola.com/computer/literature... -

Page 50: Figure 2-2. Mvme240X Debug Port Configuration

Operating Instructions SOUT RTS* DTR* CTS* DCD* PC16550 Debug MVME240x RJ45 Figure 2-2. MVME240x DEBUG Port Configuration Computer Group Literature Center Web Site... -

Page 51: Pmc Slots

MVME240x front panel provides front panel CARD I/O access to a PMC that is connected to the 64-pin connectors J21 through J24 on the MVME240x module. Connector J24 allows rear panel P2 I/O. This slot is MVME240x Port 2. http://www.motorola.com/computer/literature... -

Page 52: Pmcspan

Operating Instructions PMCspan A PMCspan front panel is pictured on the previous page. The front panel is the same for all PMCspan models. There are two PMC slots, labeled , which support PCI MEZZANINE CARD either two single-wide PMCs or one double-wide PMC. The PMCspan board has two sets of three 32-bit connectors for PMC interface to a secondary PCI bus and a user-specific I/O. -

Page 53: Introduction

Detailed descriptions of other MVME240x blocks, including programmable registers in the ASICs and peripheral chips, can be found in the MVME2400 Series VME Processor Module Programmer’s Reference Guide, listed in Appendix D, Related Documentation. - Page 54 Functional Description Table 3-1. MVME240x Features (Continued) Feature Description PCI Interface 32/64-bit Data, 33 MHz operation 8KB NVRAM with RTC and battery backup (SGS-Thomson Real-time clock M48T559) One 16550-compatible async serial port routed to front panel RJ-45 Peripheral Support 10BaseT/100BaseTX Ethernet interface routed to front panel RJ-45 Switches Reset ) and Abort...

-

Page 55: General Description

The Peripheral Component Interface (PCI) local bus is a key feature. In addition to the on-board local bus peripherals, the PCI bus supports an industry-standard mezzanine interface, IEEE P1386.1 PMC (PCI Mezzanine Card). Block Diagram Figure 3-1 is a block diagram of the MVME2400’s overall architecture. http://www.motorola.com/computer/literature... -

Page 56: Figure 3-1. Mvme240X Block Diagram

Functional Description Debug Connector SDRAM 32/64/128MB L2 Cache 512KB Flash or 1M 1MB to 9MB System Registers Processor MPC750 Hawk ASIC Clock System Memory Controller (SMC) Generator and PCI Host Bridge (PHB) 33MHz 32/64-bit PCI Local Bus Ethernet VME Bridge W83c553 Universe DEC21143... -

Page 57: Mpc750 Processor

The board is populated with 1MB of L2 cache SRAMs. The L2 cache can operate in copyback or writethru modes and supports system cache coherency through snooping. Parity generation and checking may be disabled by programming the MCP750 accordingly. Refer to the MVME2400 Programmer’s Reference Guide for additional information. http://www.motorola.com/computer/literature... -

Page 58: Hawk System Memory Controller (Smc)/Pci Host Bridge (Phb) Asic

Functional Description Hawk System Memory Controller (SMC)/PCI Host Bridge (PHB) ASIC The Hawk ASIC provides the bridge function between the MPC60x bus and the PCI Local Bus. It provides 32-bit addressing and 64-bit data. The 64-bit addressing (dual address cycle) is not supported. The Hawk supports various PowerPC processor external bus frequencies up to 100 MHz. -

Page 59: Pci Bus Latency

Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write http://www.motorola.com/computer/literature... -

Page 60: Table 3-4. Pci Originated Bandwidth Matrix

Functional Description Table 3-4. PCI Originated Bandwidth Matrix First 2 First 4 First 6 Continuous Cache Lines Cache Lines Cache Lines Clock Transaction Ratio MBytes MBytes MBytes Clks/ MBytes Clks Clks Clks Line 64-bit Writes 64-bit Reads 32-bit Writes 32-bit Reads 64-bit Writes 64-bit Reads 32-bit Writes... -

Page 61: Ppc Bus Latency

Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write Burst Read Burst Write Single Read Single Write http://www.motorola.com/computer/literature... -

Page 62: Table 3-6. Ppc60X Originated Bandwidth Matrix

Functional Description Table 3-6. PPC60x Originated Bandwidth Matrix First 2 First 4 First 6 Continuous Cache Lines Cache Lines Cache Lines Clock Transaction Ratio MBytes MBytes MBytes Clks/ MBytes Clks Clks Clks Line 64-bit Writes 64-bit Reads 32.5 32-bit Writes 32-bit Reads 42.5 64-bit Writes... -

Page 63: Assumptions

PPC60x bus is idle at the time of the start of the transaction. (that is, no pipelining effects). Cache aligned transfer, not critical word first. PCI medium responder with no zero states. One clock request/one clock grant PCI arbitration. Write posting enabled. http://www.motorola.com/computer/literature 3-11... -

Page 64: Pci Originated

Functional Description Default FIFO threshold settings Single beat writes are aligned 32-bit transfer, always executed as 32-bit PCI. Clock counts represent best case alignment between PCI and PPC60x clock domains. An exception to this is continuous bandwidth which reflects the average affects of clock alignment. PCI Originated Count represents number of PCI Bus clock cycles. -

Page 65: Sdram Latency

18 devices that total 128MB. With 128Mbit (4-bit data) devices, the block contains 256MB. When populated, these blocks appear as Block A and Block B to the Hawk. Refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide for additional information and programming details. SDRAM Latency The following table shows the performance summary for SDRAM when operating at 100 MHz using PC100 SDRAM with a CAS_latency of 2. - Page 66 Functional Description Table 3-8. 60x Bus to SDRAM Access Timing (100 MHz/PC100 SDRAMs) Access Time ACCESS TYPE Comments (tB1-tB2-tB3-tB4) 4-Beat Write after 4-Beat Write, 3-1-1-1 3-1-1-1 for the second burst write after idle. SDRAM Bank Active - Page Hit 2-1-1-1 for subsequent burst writes.

-

Page 67: Figure 3-2. Timing Definitions For Ppc Bus To Sdram Access

2. When the bus is busy and TS_ is being asserted as soon as possible after Hawk asserts AACK_ the back-to-back condition occurs. When back-to-back cycles occur, tB1 reflects the number of CLK periods from the rising edge of the CLK that samples the last TA_ http://www.motorola.com/computer/literature 3-15... -

Page 68: Flash Memory

Functional Description low of a data tenure to the rising edge of the CLK that samples the first TA_ low of the next data tenure. 3. The tB2 function reflects the number of CLK periods from the rising edge of the CLK that samples the first TA_ low in a burst data tenure to the rising edge of the CLK that samples the second TA_ low in that data tenure. -

Page 69: Rom/Flash Performance

Bits 4-Beat Read 4-Beat Write 1-Beat Read (1 byte) 1-Beat Read (2 to 8 bytes) 1-Beat Write Note The information in Table 3-9 is appropriate when configured with devices with an access time equal to 12 CLK periods. http://www.motorola.com/computer/literature 3-17... -

Page 70: Table 3-10. Ppc Bus To Rom/Flash Access Timing (80Ns @ 100 Mhz)

Functional Description Table 3-10. PPC Bus to ROM/Flash Access Timing (80ns @ 100 MHz) CLOCK PERIODS REQUIRED FOR: Total Clocks 1st Beat 2nd Beat 3rd Beat 4th Beat ACCESS TYPE Bits Bits Bits Bits Bits Bits Bits Bits Bits Bits 4-Beat Read 4-Beat Write 1-Beat Read (1 byte) -

Page 71: Ethernet Interface

In addition, the six bytes including the Ethernet station address are stored in the NVRAM (BBRAM) configuration area specified by boot ROM. That is, the value 08003E2xxxxx is stored in NVRAM. The MVME240x debugger, PPCBug, has the capability to retrieve the Ethernet station address via the CNFG command. http://www.motorola.com/computer/literature 3-19... -

Page 72: Pci Mezzanine Card (Pmc) Interface

At the physical layer, the Ethernet interface bandwidth is 10Mbit/second for 10BaseT. For the 100BaseTX, it is 100Mbit/second. Refer to the BBRAM/TOD Clock memory map description in the MVME2400 Series VME Processor Module Programmer’s Reference Guide for detailed programming information. -

Page 73: Pmc Slot 1 (Single-Width Pmc)

PMC connectors. For detailed programming information, refer to the PCI bus descriptions in the MVME2400 Series VME Processor Module Programmer’s Reference Guide and to the user documentation for the PMC modules you intend to use. -

Page 74: Pmc Slots 1 And 2 (Double-Width Pmc)

(UCSRs) for interprocessor communications. It can provide the VMEbus system controller functions as well. For detailed programming information, refer to the Universe User’s Manual and to the discussions in the MVME2400 Series VME Processor Module Programmer's Reference Guide. 3-22 Computer Group Literature Center Web Site... -

Page 75: Asynchronous Debug Port

EIA-232-D drivers and receivers to an RJ-45 connector on the front panel. The external signals are ESD protected. For detailed programming information, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide and to Texas Instrument’s data sheet #SLLS057D, dated August 1989, revised March 1996 for Asynchronous Communications Element (ACE) TL16C550A. -

Page 76: Real-Time Clock/Nvram/Timer Function

The clock generates no interrupts. Although the M48T559 is an 8-bit device, 8-, 16-, and 32-bit accesses from the ISA bus to the M48T559 are supported. Refer to the MVME2400 Series 3-24 Computer Group Literature Center Web Site... -

Page 77: Pci Host Bridge (Phb)

There are four programmable map decoders for each direction to provide flexible address mappings between the MPC and the PCI Local Bus. Refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide for additional information and programming details. Interrupt Controller (MPIC) The MPIC Interrupt Controller portion of the Hawk ASIC is designed to handle various interrupt sources. -

Page 78: Programmable Timers

For information on programming these timers, refer to the data sheet for the W83C553 PIB controller and to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. -

Page 79: Introduction

MVME240x. This includes a description of memory maps, control and status registers, PCI arbitration, interrupt handling, sources of reset, and big/little-endian issues. For additional programming information about the MVME240x, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 80: Processor Bus Memory Map

Flash bank B (socketed 1MB Flash). For detailed processor memory maps, including suggested CHRP- and PREP-compatible memory maps, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Computer Group Literature Center Web Site... -

Page 81: Pci Local Bus Memory Map

For detailed PCI memory maps, including suggested CHRP- and PREP- compatible memory maps, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. VMEbus Memory Map The VMEbus is programmable. -

Page 82: Programming Considerations

The PIB supports flexible arbitration modes of fixed priority, rotating priority, and mixed priority, as appropriate in a given application. Details on PCI arbitration can be found in the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Computer Group Literature Center Web Site... -

Page 83: Figure 4-1. Vmebus Master Mapping

RESOURCES NOTES: 1. Programmable mapping done by Hawk ASIC. 11553.00 9609 2. Programmable mapping performed via PCI Slave images in Universe ASIC. 3. Programmable mapping performed via Special Slave image (SLSI) in Universe ASIC. Figure 4-1. VMEbus Master Mapping http://www.motorola.com/computer/literature... -

Page 84: Interrupt Handling

The PCI bus (interrupts from PCI devices) The ISA bus (interrupts from ISA devices) Figure 4-2 illustrates interrupt architecture on the MVME240x. For details on interrupt handling, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Computer Group Literature Center Web Site... -

Page 85: Figure 4-2. Mvme240X Interrupt Architecture

Programming Considerations INT_ Processor (8529 Pair) MCP_ Hawk MPIC SERR_& PERR_ PCI Interrupts ISA Interrupts 11559.00 9609 Figure 4-2. MVME240x Interrupt Architecture http://www.motorola.com/computer/literature... -

Page 86: Dma Channels

Programming Details The MVME240x routes the interrupts from the PMCs and PCI expansion slots as follows: PMC Slot 1 PMC Slot 2 PCIX Slot INTA# INTB# INTC# INTD# INTA# INTB# INTC# INTD# INTA# INTB# INTC# INTD# IRQ9 IRQ10 IRQ11 IRQ12 Hawk MPIC DMA Channels The PIB supports seven DMA channels. -

Page 87: Table 4-3. Classes Of Reset And Effectiveness

Table 4-3 shows which devices are affected by the various types of resets. For details on using resets, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Table 4-3. Classes of Reset and Effectiveness... -

Page 88: Endian Issues

The following sections summarize how the MVME240x handles software and hardware differences in big- and little-endian operations. For further details on endian considerations, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Processor/Memory Domain The MPC750 processor can operate in both big-endian and little-endian mode. -

Page 89: Vmebus Domain

In little-endian mode, however, software must take the byte-swapping effect of the Universe ASIC and the address reverse-rearranging effect of the PHB into account. For further details on endian considerations, refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide. http://www.motorola.com/computer/literature 4-11... -

Page 91: Ppcbug Overview

Documentation. PPCBug Basics The PowerPC debug firmware, PPCBug, is a powerful evaluation and debugging tool for systems built around the Motorola PowerPC microcomputers. Facilities are available for loading and executing user programs under complete operator control for system evaluation. PPCBug provides a high degree of functionality, user friendliness, portability, and ease of maintenance. - Page 92 PPCBug PPCBug includes commands for: Display and modification of memory Breakpoint and tracing capabilities A powerful assembler and disassembler useful for patching programs A self-test at power-up feature which verifies the integrity of the system PPCBug consists of three parts: 1.

-

Page 93: Memory Requirements

1. Sets MPU.MSR to known value. 2. Invalidates the MPU’s data/instruction caches. 3. Clears all segment registers of the MPU. 4. Clears all block address translation registers of the MPU. 5. Initializes the MPU-bus-to-PCI-bus bridge device. 6. Initializes the PCI-bus-to-ISA-bus bridge device. http://www.motorola.com/computer/literature... - Page 94 PPCBug 7. Calculates the external bus clock speed of the MPU. 8. Delays for 750 milliseconds. 9. Determines the CPU base board type. 10. Sizes the local read/write memory (that is, DRAM). 11. Initializes the read/write memory controller. Sets base address of memory to $00000000.

-

Page 95: Using Ppcbug

What you key in is stored in an internal buffer. Execution begins only after you press the Return or Enter key. This allows you to correct entry errors, if necessary, with the control characters described in the PPCBug Firmware Package User’s Manual. http://www.motorola.com/computer/literature... -

Page 96: Debugger Commands

PPCBug After the debugger executes the command, the prompt reappears. However, if the command causes execution of user target code (for example GO) then control may or may not return to the debugger, depending on what the user program does. For example, if a breakpoint has been specified, then control returns to the debugger when the breakpoint is encountered during execution of the user program. -

Page 97: Table 5-1. Debugger Commands

Configure Board Information Block Checksum CSAR PCI Configuration Space READ Access CSAW PCI Configuration Space WRITE Access Data Conversion One Line Disassembler Dump S-Records ECHO Echo String Set Environment FORK Fork Idle MPU at Address FORKWR Fork Idle MPU with Registers http://www.motorola.com/computer/literature... - Page 98 PPCBug Table 5-1. Debugger Commands (Continued) Command Description Go Direct (Ignore Breakpoints) GEVBOOT Global Environment Variable Boot GEVDEL Global Environment Variable Delete GEVDUMP Global Environment Variable(s) Dump GEVEDIT Global Environment Variable Edit GEVINIT Global Environment Variable Initialization GEVSHOW Global Environment Variable(s) Display Go to Next Instruction G, GO Go Execute User Program...

- Page 99 Offset Registers Display/Modify Printer Attach NOPA Printer Detach PBOOT Bootstrap Operating System Port Format NOPF Port Detach PFLASH Program FLASH Memory Put RTC into Power Save Mode ROMboot Enable NORB ROMboot Disable Register Display REMOTE Remote RESET Cold/Warm Reset http://www.motorola.com/computer/literature...

- Page 100 PPCBug Table 5-1. Debugger Commands (Continued) Command Description Read Loop Register Modify Register Set MPU Execution/Status Switch Directories Set Time and Date SROM SROM Examine/Modify Symbol Table Attach NOSYM Symbol Table Detach SYMS Symbol Table Display/Search Trace Terminal Attach TIME Display Time and Date Transparent Mode Trace to Temporary Breakpoint...

-

Page 101: Diagnostic Tests

MVME240x. Using the HE command, you can list the diagnostic routines available in each test group. Refer to the PPCBug Diagnostics Manual for complete descriptions of the diagnostic routines and instructions on how to invoke them. http://www.motorola.com/computer/literature 5-11... -

Page 102: Table 5-2. Diagnostic Test Groups

PPCBug Table 5-2. Diagnostic Test Groups Test Group Description CL1283 Parallel Interface (CL1283) Tests* DEC21x43 Ethernet Controller Tests HAWK HAWK Tests ISABRDGE PCI/ISA Bridge Tests KBD8730x PC8730x Keyboard/Mouse Tests* L2CACHE Level 2 Cache Tests NCR 53C8xx SCSI-2 I/O Processor Tests PAR8730x Parallel Interface (PC8730x) Test* UART... -

Page 103: Overview

6Environment Modification Overview You can use the factory-installed debug monitor, PPCBug, to modify certain parameters contained in the MVME240x’s Non-Volatile RAM (NVRAM), also known as Battery Backed-up RAM (BBRAM). The Board Information Block in NVRAM contains various elements concerning operating parameters of the hardware. Use the PPCBug command CNFG to change those parameters. -

Page 104: Cnfg - Configure Board Information Block

The Board Information Block is factory-configured before shipment. There is no need to modify block parameters unless the NVRAM is corrupted. Refer to the MVME2400 Series VME Processor Module Programmer’s Reference Guide, listed in Appendix D, Related Documentation, for the actual location and other information about the Board Information Block. -

Page 105: Env - Set Environment

Refer to the PPCBug Firmware Package User’s Manual for a description of the use of ENV. Additional information on registers in the Universe ASIC that affect these parameters is contained in your MVME2400 Series VME Processor Module Programmer’s Reference Guide. - Page 106 Environment Modification Remote Start Method Switch [G/M/B/N] = B? The Remote Start Method Switch is used when the MVME2400 is cross-loaded from another VME-based CPU, to start execution of the cross-loaded program. Use the Global Control and Status Register to pass and start execution of the cross-loaded program.

- Page 107 Primary SCSI Bus Negotiations Type [A/S/N] = A? Asynchronous SCSI bus negotiation. (Default) Synchronous SCSI bus negotiation. None. Primary SCSI Data Bus Width [W/N] = N? Wide SCSI (16-bit bus). Narrow SCSI (8-bit bus). (Default) Secondary SCSI identifier = 07? Select the identifier. (Default = 07.) http://www.motorola.com/computer/literature...

- Page 108 Environment Modification NVRAM Bootlist (GEV.fw-boot-path) Boot Enable [Y/N] = N? Give boot priority to devices defined in the fw-boot- path global environment variable (GEV). Do not give boot priority to devices listed in the fw- boot-path GEV. (Default) Note When enabled, the GEV (Global Environment Variable) boot takes priority over all other boots, including Autoboot and Network Boot.

-

Page 109

The time in seconds that the Autoboot sequence will delay before starting the boot. The purpose for the delay is to allow you the option of stopping the boot by use of the

key. The time value is from 0-255 seconds. (Default = 7 seconds) http://www.motorola.com/computer/literature... - Page 110 Environment Modification Auto Boot Default String [NULL for an empty string] = ? You may specify a string (filename) which is passed on to the code being booted. The maximum length of this string is 16 characters. (Default = null string) ROM Boot Enable [Y/N] = N? The ROMboot function is enabled.

- Page 111 The address where the network interface configuration parameters are to be saved/retained in NVRAM; these parameters are the necessary parameters to perform an unattended network boot. A typical offset might be $1000, but this value is application-specific. (Default = $00001000) http://www.motorola.com/computer/literature...

- Page 112 Environment Modification If you use the NIOT debugger command, these parameters need to be saved somewhere in the offset range $00001000 through $000016F7. The NIOT parameters do not exceed 128 bytes in size. The setting of this ENV Caution pointer determines their location. If you have used the same space for your own program information or commands, they will be overwritten and lost.

- Page 113 The configured value is ignored by PPCBug. DRAM Parity Enable [On-Detection/Always/Never - O/A/N] = O? DRAM parity is enabled upon detection. (Default) DRAM parity is always enabled. DRAM parity is never enabled. Note This parameter (above) also applies to enabling ECC for DRAM. http://www.motorola.com/computer/literature 6-11...

- Page 114 PIRQ0/1/2/3. The default is determined by system type. For details on PCI/ISA interrupt assignments and for suggested values to enter for this parameter, refer to the 8259 Interrupts section of the MVME2400 Series VME Processor Module Programmer’s Reference Guide. Note...

-

Page 115: Configuring The Vmebus Interface

ENV asks the following series of questions to set up the VMEbus interface for the MVME240x modules. To perform this configuration, you should have a working knowledge of the Universe ASIC as described in your MVME2400 Series VME Processor Module Programmer’s Reference Guide. VME3PCI Master Master Enable [Y/N] = Y? Set up and enable the VMEbus Interface. - Page 116 Environment Modification PCI Slave Image 1 Bound Address Register = 20000000? The configured value is written into the LSI1_BD register of the Universe chip. PCI Slave Image 1 Translation Offset = 00000000? The configured value is written into the LSI1_TO register of the Universe chip.

- Page 117 VMEbus Slave Image 1 Translation Offset = 00000000? The configured value is written into the VSI1_TO register of the Universe chip. VMEbus Slave Image 2 Control = 00000000? The configured value is written into the VSI2_CTL register of the Universe chip. http://www.motorola.com/computer/literature 6-15...

- Page 118 Environment Modification VMEbus Slave Image 2 Base Address Register = 00000000? The configured value is written into the VSI2_BS register of the Universe chip. VMEbus Slave Image 2 Bound Address Register = 00000000? The configured value is written into the VSI2_BD register of the Universe chip.

- Page 119 ENV – Set Environment Miscellaneous Control Register = 52060000? The configured value is written into the MISC_CTL register of the Universe chip. User AM Codes = 00000000? The configured value is written into the USER_AM register of the Universe chip. http://www.motorola.com/computer/literature 6-17...

-

Page 121: Appendix A Specifications

ASpecifications Specifications The following table lists the general specifications for the MVME240x VME processor module. The later sections provide information on cooling requirements and EMC regulatory compliance. Specifications for the optional PMCs can be found in the documentation for those modules. Table A-1. - Page 122 Specifications Table A-1. Specifications (Continued) Characteristics Specifications Relative humidity 10% to 90% NC (Non-Condensing) Vibration (operating) 1 G RMS, 20 Hz-2000 Hz random Altitude (operating) 5000 meters (16,405 feet) Physical dimensions Height Double-high VME board, 9.2 in. (233 mm) (base board only) Front panel width 0.8 in.

-

Page 123: Cooling Requirements

131° F) with forced air cooling of the entire assembly (base board and modules) at a velocity typically achievable by using a 100 CFM axial fan. Temperature qualification is performed in a standard Motorola VMEsystem chassis. Twenty-five-watt load boards are inserted in two card slots (one on each side adjacent to the board under test) to simulate a high power density system configuration. -

Page 124: Emc Regulatory Compliance

Specifications While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources, adequate cooling can usually be achieved with 10 CFM and 490 LFM flowing over the module. Less airflow is required to cool the module in environments having lower maximum ambients. -

Page 125: Introduction

BConnector Pin Assignments Introduction This appendix provides the pin assignments for the following groups of interconnect signals for the MVME240x: Connector Location Table VMEbus connector Table B-1 VMEbus connector, P2 I/O Table B-2 Debug serial port, RJ-45 DEBUG (J2) Table B-3 Ethernet port, RJ-45 10/100BASET (J3) Table B-4... -

Page 126: Vmebus Connector - P1

Connector Pin Assignments VMEbus Connector – P1 Two 160-pin DIN type connectors, P1 and P2, supply the interface between the base board and the VMEbus. P1 provides power and VME signals for 24-bit addressing and 16-bit data. Its pin assignments are set by the IEEE P1014-1987 VMEbus Specification and the VME64 Extension Standard. -

Page 127: Vmebus Connector - P2

PMC2_10 (J24-10) PMC1_16 (J14-16) VA28 PMC1_15 (J14-15) PMC2_12 (J24-12) PMC2_14 (J24-14) PMC1_18 (J14-18) VA29 PMC1_17 (J14-17) PMC2_13 (J24-13) PMC1_20 (J14-20) VA30 PMC1_19 (J14-19) PMC2_15 (J24-15) PMC2_17 (J24-17) PMC1_22 (J14-22) VA31 PMC1_21 (J14-21) PMC2_16 (J24-16) PMC1_24 (J14-24) PMC1_23 (J14-23) PMC2_18 (J24-18) http://www.motorola.com/computer/literature... - Page 128 Connector Pin Assignments Table B-2. P2 Connector Pin Assignment (Continued) PMC2_20 (J24-20) PMC1_26 (J14-26) PMC1_25 (J14-25) PMC2_19 (J24-19) PMC1_28 (J14-28) VD16 PMC1_27 (J14-27) PMC2_21 (J24-21) PMC2_23 (J24-23) PMC1_30 (J14-30) VD17 PMC1_29 (J14-29) PMC2_22 (J24-22) PMC1_32 (J14-32) VD18 PMC1_31 (J14-31) PMC2_24 (J24-24) PMC2_26 (J24-26) PMC1_34 (J14-34) VD19...

-

Page 129: Serial Port Connector - Debug (J2

The 10BaseT/100BaseTx connector is an RJ-45 connector located on the front plate of the MVME240x. The pin assignments for this connector are as follows: Table B-4. 10/100 BASET (J3) Connector Pin Assignments TD– No Connect No Connect RD– No Connect No Connect http://www.motorola.com/computer/literature... -

Page 130: Cpu Debug Connector - J1

Connector Pin Assignments CPU Debug Connector – J1 One 190-pin Mictor connector with center row of power and ground pins is used to provide access to the Processor Bus and some miscellaneous signals. The pin assignments for this connector are as follows: Table B-5. - Page 131 Pin Assignments Table B-5. Debug Connector Pin Assignments (Continued) PD10 PD11 PD12 PD13 PD14 PD15 PD16 PD17 PD18 PD19 PA20 PD21 PD22 PD23 PD24 PD25 PD26 PD27 PD28 PD29 PD30 PD31 PD32 PD33 PD34 PD35 PD36 PD37 http://www.motorola.com/computer/literature...

- Page 132 Connector Pin Assignments Table B-5. Debug Connector Pin Assignments (Continued) PD38 PD39 PD40 PD41 PD42 PD43 PD44 PD45 PD46 PD47 PD48 PD49 PA50 PD51 PD52 PD53 PD54 PD55 PD56 PD57 PD58 PD59 PD60 PD61 PD62 PD63 PDPAR0 PDPAR1 PDPAR2 PDPAR3 PDPAR4 PDPAR5 PDPAR6...

- Page 133 Pin Assignments Table B-5. Debug Connector Pin Assignments (Continued) +3.3V TSIZ0 TSIZ1 TSIZ2 CSE0 GLOBAL# CSE1 SHARED# DBWO# AACK# ARTY# XATS# DRTY# TBST# TEA# DBG# DBB# ABB# TCLK_OUT CPUGNT0# CPUREQ0# http://www.motorola.com/computer/literature...

- Page 134 Connector Pin Assignments Table B-5. Debug Connector Pin Assignments (Continued) CPUREQ1# INT0# CPUGNT1# MCPI# INT1# SMI# MCPI1# CKSTPI# L2BR# CKSTPO# L2BG# HALTED L2CLAIM# TLBISYNC# TBEN SUSPEND# DRVMOD0 DRVMOD1 NAPRUN SRESET1# QREQ# SRESET0# QACK# HRESET# CPUCLK CPUCLK CPUCLK TRST# B-10 Computer Group Literature Center Web Site...

-

Page 135: Pci Expansion Connector - J6

Table B-6. J6 - PCI Expansion Connector Pin Assignments +3.3V +3.3V PCICLK PMCINTA# PMCINTB# PURST# PMCINTC# HRESET# PMCINTD# TRST# PCIXP# PCIXGNT# PCIXREQ# +12V –12V PERR# SERR# LOCK# SDONE DEVSEL# SBO# TRDY# IRDY# STOP# FRAME# ACK64# Reserved REQ64# Reserved http://www.motorola.com/computer/literature B-11... - Page 136 Connector Pin Assignments Table B-6. J6 - PCI Expansion Connector Pin Assignments (Continued) PCIRST# C/BE1# C/BE0# C/BE3# C/BE2# AD11 AD10 AD13 AD12 AD15 AD14 AD17 AD16 AD19 AD18 AD21 AD20 AD23 AD22 AD25 AD24 AD27 AD26 AD29 AD28 AD31 AD30 B-12 Computer Group Literature Center Web Site...

- Page 137 PAR64 Reserved C/BE5# C/BE4# C/BE7# C/BE6# AD33 AD32 AD35 AD34 AD37 AD36 AD39 AD38 AD41 AD40 AD43 AD42 AD45 AD44 AD47 AD46 AD49 AD48 AD51 AD50 AD53 AD52 AD55 AD54 AD57 AD56 AD59 AD58 AD61 AD60 AD63 AD62 http://www.motorola.com/computer/literature B-13...

-

Page 138: Pci Mezzanine Card Connectors - J11 Through J14

Connector Pin Assignments PCI Mezzanine Card Connectors – J11 through J14 Four 64-pin SMT connectors, J11 through J14, supply 32/64-bit PCI interfaces and P2 I/O between the MVME240x board and an optional add- on PCI Mezzanine Card (PMC) in PMC Slot 1. The pin assignments for PMC Slot 1 are listed in the following two tables. -

Page 139: Table B-8. J13 - J14 Pmc1 Connector Pin Assignments

AD55 AD54 PMC1_23 (P2-C12) PMC1_24 (P2-A12) AD53 PMC1_25 (P2-C13) PMC1_26 (P2-A13) AD52 PMC1_27 (P2-C14) PMC1_28 (P2-A14) AD51 AD50 PMC1_29 (P2-C15) PMC1_30 (P2-A15) AD49 PMC1_31 (P2-C16) PMC1_32 (P2-A16) AD48 PMC1_33 (P2-C17) PMC1_34 (P2-A17) AD47 AD46 PMC1_35 (P2-C18) PMC1_36 (P2-A18) http://www.motorola.com/computer/literature B-15... - Page 140 Connector Pin Assignments Table B-8. J13 - J14 PMC1 Connector Pin Assignments (Continued) AD45 PMC1_37 (P2-C19) PMC1_38 (P2-A19) +5V (Vio) AD44 PMC1_39 (P2-C20) PMC1_40 (P2-A20) AD43 AD42 PMC1_41 (P2-C21) PMC1_42 (P2-A21) AD41 PMC1_43 (P2-C22) PMC1_44 (P2-A22) AD40 PMC1_45 (P2-C23) PMC1_46 (P2-A23) AD39 AD38 PMC1_47 (P2-C24)

-

Page 141: Pci Mezzanine Card Connectors - J21 Through J24

AD25 AD24 +3.3V C/BE3# IDSEL2 AD23 AD22 AD21 +3.3V AD20 AD19 AD18 +5V (Vio) AD17 AD16 C/BE2# FRAME# Not Used IRDY# TRDY# +3.3V DEVSEL# STOP# LOCK# PERR# SDONE# SBO# +3.3V SERR# C/BE1# AD15 AD14 AD13 AD12 AD11 AD10 http://www.motorola.com/computer/literature B-17... -

Page 142: Table B-10. J23 And J24 Pmc2 Connector Pin Assignments

Connector Pin Assignments Table B-9. J21 and J22 PMC2 Connector Pin Assignments (Continued) AD09 +5V (Vio) AD08 +3.3V C/BE0# AD07 Not Used AD06 AD05 +3.3V Not Used AD04 Not Used AD03 Not Used Not Used AD02 AD01 Not Used AD00 +5V (Vio) ACK64# +3.3V... - Page 143 Not Used Not Used AD35 AD34 Not Used Not Used AD33 Not Used Not Used +5V (Vio) AD32 Not Used Not Used Reserved Reserved Not Used Not Used Reserved Not Used Not Used Reserved Not Used Not Used http://www.motorola.com/computer/literature B-19...

-

Page 145: Appendix C Troubleshooting

CTroubleshooting Solving Startup Problems In the event problems arise with the operation of your module, perform the troubleshooting steps in this appendix prior to calling for help or sending the board back for repair. Some of the procedures will return the board to the factory debugger environment. - Page 146 Troubleshooting Table C-1. Troubleshooting MVME240x Modules (Continued) Condition Possible Problem Try This: II. There is a display A. The keyboard or Recheck the keyboard and/or mouse connections on the terminal, mouse may be and power. but input from the connected keyboard and/or incorrectly.

- Page 147 The date and time will be board does not set incorrectly. displayed. autoboot. B. There may be some fault in the board hardware. Performing the next step (env;d) will change some parameters that may affect your system’s Caution operation. (continues>) http://www.motorola.com/computer/literature...

-

Page 148

Troubleshooting Table C-1. Troubleshooting MVME240x Modules (Continued) Condition Possible Problem Try This: IV. Continued 2. At the command line prompt, type in: env;d

This sets up the default parameters for the debugger environment. 3. When prompted to Update Non-Volatile RAM, type in: y ... - Page 149 1. Document the problem and return the board for failed one or more some fault in the service. of the tests listed board hardware or 2. Phone 1-800-222-5640. above, and cannot the on-board be corrected using debugging and the steps given. diagnostic firmware. TROUBLESHOOTING PROCEDURE COMPLETE. http://www.motorola.com/computer/literature...

-

Page 151: Motorola Computer Group Documents

DRelated Documentation Motorola Computer Group Documents The Motorola publications listed below are referenced in this manual. You can obtain paper or electronic copies of Motorola Computer Group publications by: Contacting your local Motorola sales office Visiting MCG’s World Wide Web literature site http://www.motorola.com/computer/literature... -

Page 152: Manufacturers' Documents

Table D-2. Manufacturers’ Documents Publication Document Title and Source Number PowerPC 750 RISC Microprocessor Technical Summary MPC750/D Literature Distribution Center for Motorola Telephone: 1-800- 441-2447 FAX: (602) 994-6430 or (303) 675-2150 Web Site: http://e-www.motorola.com/webapp/DesignCenter/ E-mail: [email protected] PowerPC 750 RISC Microprocessor User’s Manual... - Page 153 W83C553 Enhanced System I/O Controller with PCI Arbiter (PIB) W83C553F Winbond Electronics Corporation; Web Site: http://www.winbond.com.tw/product/ M48T59 CMOS 8K x 8 TIMEKEEPER SRAM Data Sheet M48T59 STMicroelectronics; Web Site: http://eu.st.com/stonline/index.shtml Universe User Manual 8091042_MD300_ 05.pdf Tundra Semiconductor Corporation Web Site: http://www.tundra.com/page.cfm?tree_id=100008#Universe II (CA91C042) http://www.motorola.com/computer/literature...

-

Page 154: Related Specifications

Related Documentation Related Specifications For additional information, refer to the following table for related specifications. For your convenience, a source for the listed document is also provided. It is important to note that in many cases, the information is preliminary and the revision levels of the documents are subject to change without notice. - Page 155 Document Title and Source Publication Number PowerPC Microprocessor Common Hardware Reference Platform: A System Architecture (CHRP), Version 1.0 Literature Distribution Center for Motorola Telephone: 1-800- 441-2447 FAX: (602) 994-6430 or (303) 675-2150 Web Site: http://e-www.motorola.com/webapp/DesignCenter/ E-mail: [email protected] Morgan Kaufmann Publishers, Inc.

- Page 157 Glossary An Ethernet implementation in which the physical medium is a 10Base-5 doubly shielded, 50-ohm coaxial cable capable of carrying data at 10 Mbps for a length of 500 meters (also referred to as thicknet). Also known as thick Ethernet. An Ethernet implementation in which the physical medium is a 10Base-2 single-shielded, 50-ohm RG58A/U coaxial cable capable of...

- Page 158 Glossary big-endian A byte-ordering method in memory where the address n of a word corresponds to the most significant byte. In an addressed memory word, the bytes are ordered (left to right) 0, 1, 2, 3, with 0 being the most significant byte.

- Page 159 The Green signals (G-Y) can be extracted by these two signals. Common Hardware Reference Platform (CHRP) A specification published by Apple, IBM, and Motorola which defines the devices, interfaces, and data formats that make up a CHRP-compliant system using a PowerPC processor.

- Page 160 The code name for the DRAM controller chip developed by Falcon Motorola for the MVME2600 and MVME3600 series of boards. It is intended to be used in sets of two to provide the necessary interface between the Power PC60x bus and the 144-bit ECC DRAM (system memory array) and/or ROM/Flash.

- Page 161 A graphics system in which the even scanlines are refreshed in one interlaced vertical cycle (field), and the odd scanlines are refreshed in another vertical cycle. The advantage is that the video bandwidth is roughly half that required for a non-interlaced system of the same resolution. http://www.motorola.com/computer/literature GL-5...

- Page 162 Musical Instrument Digital Interface. The standard format for MIDI recording, storing, and playing digital music. Multimedia Personal Computer The PowerPC-to-PCI bus bridge chip developed by Motorola for the MPC105 Ultra 603/Ultra 604 system board. It provides the necessary interface between the MPC603/MPC604 processor and the Boot ROM (secondary cache), the DRAM (system memory array), and the PCI bus.

- Page 163 MPC601 Motorola’s component designation for the PowerPC 601 microprocessor. Motorola’s component designation for the PowerPC 603 MPC603 microprocessor. MPC604 Motorola’s component designation for the PowerPC 604 microprocessor. MPIC Multi-Processor Interrupt Controller MicroProcessing Unit Mean Time Between Failures. A statistical term relating to MTBF reliability as expressed in power on hours (poh).

- Page 164 Glossary palette The range of colors available on the screen, not necessarily simultaneously. For VGA, this is either 16 or 256 simultaneous colors out of 262,144. A connector that can exchange data with an I/O device eight bits at parallel port a time.

- Page 165 PowerPC is used by Motorola, Inc. under license from IBM. The first implementation of the PowerPC family of PowerPC 601™ microprocessors. This CPU incorporates a memory management unit with a 256-entry buffer and a 32KB unified (instruction and data) cache.

- Page 166 Glossary Row Address Strobe. A clock signal used in dynamic RAMs to control the input of the row addresses. The PowerPC-to-PCI local bus bridge chip developed by Motorola Raven for the MVME2600 and MVME3600 series of boards. It provides the necessary interface between the PowerPC 60x bus and the PCI bus, and acts as interrupt controller.

- Page 167 Ethernet See 10BaseT. twisted-pair Ethernet UART Universal Asynchronous Receiver/Transmitter ASIC developed by Tundra in consultation with Motorola, that Universe provides the complete interface between the PCI bus and the 64-bit VMEbus. UltraViolet Ultra Video Graphics Array. An improved VGA monitor standard...

- Page 168 When data is copied from disk to main memory, the physical address is changed to the virtual address. VL bus See VESA Local bus (VL bus). MCG second generation VMEbus interface ASIC (Motorola) VMEchip2 MCG ASIC that interfaces between the PCI bus and the VMEchip2 VME2PCI device.

- Page 169 Index Numerics MVME240x board 10/100 BASET port configuration 16/32-bit timers 3-26 board information block board placement 1-20 abort (interrupt) signal board structure ABT switch (S1) bridge altitude (operating) as Hawk function ambient air temperature architecture basics MVME240x buses, standard 3-3, assembly language asynchronous debug port 3-23...

- Page 170 Index Auto Boot Default String Auto Boot Device CPU LED (DS2) 2-3, Auto Boot Partition Number L2 Cache Parity Enable 6-12 Memory Size 6-10 debug console terminal Negate VMEbus SYSFAIL* Always debug firmware, PPCBug Network Auto Boot Controller DEBUG port 1-21 NVRAM Bootlist debug port...

- Page 171 VMEbus interconnect signals xvii, memory size 6-10 interface Memory Size Enable 6-10 Ethernet 3-19 memory sizes PCI bus 3-20 SDRAM 3-12 VMEbus 3-22 Motorola Computer Group documents interrupt architecture, MVME230x MPC750 processor Interrupt Controller (MPIC) 3-25 interrupt support http://www.motorola.com/computer/literature IN-3...

- Page 172 Index MPIC (MultiProcessor Interrupt Controller) parameter (Negate VMEbus SYSFAIL* 3-25 Always) MPU initialization parameter (Network Auto Boot Control- MPU specifications ler) MVME230x parameter (NVRAM Bootlist) EMC regulatory compliance parameter (Primary SCSI Bus Negotia- specifications tions) MVME240x parameter (Primary SCSI Data Bus cooling requirements Width) installing...

- Page 173 3-24 preparing 1-11 Real-Time Clock/NVRAM/timer function PMCspan 1-11, 3-24 preparing 1-11 regulatory guidelines PMCspan Expansion Mezzanine related documentation, ordering PMCspan-002 Installation related specifications MVME240x 1-16 remote control/status connector 3-26 port required equipment asynchronous 3-23 reset debug 3-23 http://www.motorola.com/computer/literature IN-5...

- Page 174 Index resetting the system 2-3, 1-10 restart mode 5-12 switch S3 1-11 RF emissions switches ROM Boot Enable switches, MVME240x front panel ROM First Access Length 6-10 SYSFAIL* ROMboot enable 6-8, 6-11, 6-12 system console terminal ROMFAL 6-10 system console, connecting 1-21 ROMNAL system controller...

- Page 175 (J9) Universe ASIC 3-22 VMEbus interface 6-13 VMEsystem enclosure Winbond PCI/ISA bus bridge controller 3-23, Winbond W83C553 as PCI arbiter support http://www.motorola.com/computer/literature IN-7...